【導(dǎo)讀】在商業(yè)、工業(yè)及汽車電子領(lǐng)域,高溫環(huán)境對(duì)集成電路的性能、可靠性和安全性構(gòu)成嚴(yán)峻挑戰(zhàn)。隨著應(yīng)用場(chǎng)景向極端溫度條件延伸,高結(jié)溫引發(fā)的漏電增加、壽命衰減等問題日益凸顯,亟需通過創(chuàng)新設(shè)計(jì)技術(shù)突破技術(shù)瓶頸。本文將解析高溫對(duì)集成電路的深層影響,揭示高結(jié)溫帶來的五大核心挑戰(zhàn),并探討針對(duì)性的高功率設(shè)計(jì)解決方案。

在商業(yè)、工業(yè)及汽車電子領(lǐng)域,高溫環(huán)境對(duì)集成電路的性能、可靠性和安全性構(gòu)成嚴(yán)峻挑戰(zhàn)。隨著應(yīng)用場(chǎng)景向極端溫度條件延伸,高結(jié)溫引發(fā)的漏電增加、壽命衰減等問題日益凸顯,亟需通過創(chuàng)新設(shè)計(jì)技術(shù)突破技術(shù)瓶頸。本文將解析高溫對(duì)集成電路的深層影響,揭示高結(jié)溫帶來的五大核心挑戰(zhàn),并探討針對(duì)性的高功率設(shè)計(jì)解決方案。

高結(jié)溫帶來的挑戰(zhàn)

半導(dǎo)體器件在較高溫度下工作會(huì)降低電路性能,縮短使用壽命。對(duì)于硅基半導(dǎo)體而言,晶體管參數(shù)會(huì)隨著溫度的升高而下降,由于本征載流子密度的影響,最高極限會(huì)低于 300℃。依靠選擇性摻雜的器件可能會(huì)失效或性能不佳。

影響 IC 在高溫下工作的主要技術(shù)挑戰(zhàn)包括:

? 泄漏電流增加

? MOS 晶體管閾值電壓降低

? 載流子遷移率降低

? 提高閂鎖效應(yīng)(Latch-Up)敏感性

? 加速損耗機(jī)制

? 對(duì)封裝和接合可靠性的挑戰(zhàn)

要設(shè)計(jì)出能夠在高溫下工作的 IC,了解高溫下面臨的挑戰(zhàn)至關(guān)重要。下文將探討 IC 設(shè)計(jì)面臨的挑戰(zhàn)。

1.泄漏電流增加

CMOS 電路中泄漏電流的增加主要是由半導(dǎo)體 PN 結(jié)泄漏和亞閾值溝道泄漏的增加引起的。

?反向偏置 PN 結(jié)泄漏

在較高溫度下,半導(dǎo)體中熱能的增加會(huì)導(dǎo)致更多電子 - 空穴對(duì)的產(chǎn)生,從而產(chǎn)生更高的泄露電流。結(jié)泄漏取決于摻雜水平,通常隨溫度呈指數(shù)增長(zhǎng)。根據(jù)廣泛使用的經(jīng)驗(yàn)法則,溫度每升高 10℃,結(jié)電流大約增加一倍。

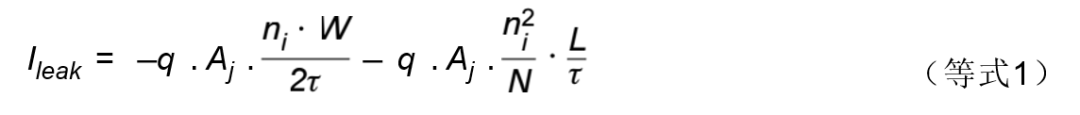

二極管的泄漏電流由漂移電流和擴(kuò)散電流組成:

其中, q 為電子的基本電荷, Aj 為結(jié)面積,ni 為本征載流子濃度,W 為耗盡區(qū)寬度,τ 為有效少數(shù)載流子壽命,L 為擴(kuò)散長(zhǎng)度,N 為中性區(qū)摻雜密度。

在中等溫度下,泄漏電流主要由耗盡區(qū)中電子 - 空穴對(duì)產(chǎn)生的熱引起。在高溫下,泄漏電流主要由中性區(qū)產(chǎn)生的少數(shù)載流子引起。漂移電流與耗盡區(qū)寬度成正比,這意味著它與結(jié)電壓的平方根成正比(在正常反向電壓下),而擴(kuò)散電流與結(jié)電壓無關(guān),并且與摻雜密度 N 成反比。摻雜水平越高,在溫度高于約 150°C 時(shí)擴(kuò)散泄漏越少。

泄漏電流的指數(shù)增加影響了大多數(shù)主動(dòng)器件(如雙極晶體管、MOS 晶體管、二極管)和一些被動(dòng)器件(如擴(kuò)散電容、電阻)。然而,由氧化物隔離的器件,例如多晶硅電阻、多晶硅二極管、ploy-poly 電容和 metal-metal 電容,并不受結(jié)泄漏的影響。結(jié)泄漏被認(rèn)為是高溫 bulk CMOS 電路中最嚴(yán)峻的挑戰(zhàn)。

?亞閾值溝道泄漏

MOS 晶體管關(guān)閉時(shí),柵極 - 源極電壓 VGS 通常設(shè)置為零。由于漏極至源極電壓 VDS 非零,因此漏極和源極之間會(huì)有小電流流過。當(dāng) Vgs 低于閾值電壓 Vt 時(shí),即在亞閾值或弱反型區(qū),就會(huì)發(fā)生亞閾值泄漏。該區(qū)域的漏極源極電流并不為零,而是與 Vgs 呈指數(shù)關(guān)系,主要原因是少數(shù)載流子的擴(kuò)散。

該電流在很大程度上取決于溫度、工藝、晶體管尺寸和類型。短溝道晶體管的電流會(huì)增大,閾值電壓較高的晶體管的電流會(huì)減小。亞閾值斜率因子 S 描述了晶體管從關(guān)斷(低電流)切換到導(dǎo)通(高電流)的有效程度,定義為使漏極電流變化十倍所需改變的 VGS 的變化量:

其中,n 是亞閾值斜率系數(shù)(通常約為 1.5)。對(duì)于 n = 1,斜率因子為 60mV/10 倍,這意味著每低于閾值電壓 Vt 60mV,漏極電流就會(huì)減少十倍。典型的 n = 1.5 意味著電流下降速度較慢,為 90mV/10 倍。為了能夠有效地關(guān)閉 MOS 晶體管并減少亞閾值泄漏,柵極電壓必須降到足夠低于閾值電壓的水平。

?柵極氧化層隧穿泄露

對(duì)于極薄的柵極氧化層(厚度低于約 3 納米),必須考慮隧穿泄漏電流的影響。這種電流與溫度有關(guān),由多種機(jī)制引發(fā)。Fowler-Nordheim 遂穿是在高電場(chǎng)作用下,電子通過氧化層形成的三角形勢(shì)壘時(shí)產(chǎn)生。隨著有效勢(shì)壘高度降低,隧道電流隨溫度升高而增大。較高的溫度也會(huì)增強(qiáng) trap-assisted 隧穿現(xiàn)象,即電子借助氧化層中的中間陷阱態(tài)通過。對(duì)于超薄氧化層,直接隧穿變得顯著,由于電子熱能的增加,隧穿概率也隨之上升。

2.閾值電壓降低

MOS 晶體管的閾值電壓 Vt 與溫度密切相關(guān),通常隨著溫度的升高而線性降低。這是由于本征載流子濃度增加、半導(dǎo)體禁帶變窄、半導(dǎo)體 - 氧化物界面的表面電位的變化以及載流子遷移率降低等因素造成的。溫度升高導(dǎo)致的閾值電壓降低會(huì)引起亞閾值漏電流呈指數(shù)增長(zhǎng)。

3.載流子遷移率下降

載流子遷移率直接影響 MOS 晶體管的性能,其受晶格散射與雜質(zhì)散射的影響。溫度升高時(shí),晶格振動(dòng)(聲子)加劇,導(dǎo)致電荷載流子的散射更加頻繁,遷移率隨之下降。此外,高溫還會(huì)增加本征載流子濃度,引發(fā)更多的載流子 - 載流子散射,進(jìn)一步降低遷移率。當(dāng)溫度從 25°C 升高到 200°C 時(shí),載流子遷移率大約會(huì)減半。

載流子遷移率顯著影響多個(gè)關(guān)鍵的 MOS 參數(shù)。載流子遷移率的下降會(huì)降低驅(qū)動(dòng)電流,減少晶體管的開關(guān)速度和整體性能。更高的導(dǎo)通電阻會(huì)增加功率損耗并降低效率。較低的遷移率還會(huì)降低跨導(dǎo),使亞閾值斜率變緩(增加亞閾值泄漏),降低載流子飽和速度(對(duì)于短溝道器件至關(guān)重要),并間接影響閾值電壓。

4.提高閂鎖效應(yīng)敏感性

集成電路中各個(gè)二極管、晶體管和其他元件之間的隔離是通過反向偏置 P-N 結(jié)來實(shí)現(xiàn)的。在電路開發(fā)過程中,需采取預(yù)防措施以確保這些結(jié)在預(yù)期應(yīng)用條件下始終可靠阻斷。這些 P-N 結(jié)與其他相鄰結(jié)形成 N-P-N 和 P-N-P 結(jié)構(gòu),從而產(chǎn)生寄生 NPN 或 PNP 晶體管,這些晶體管可能會(huì)被意外激活。

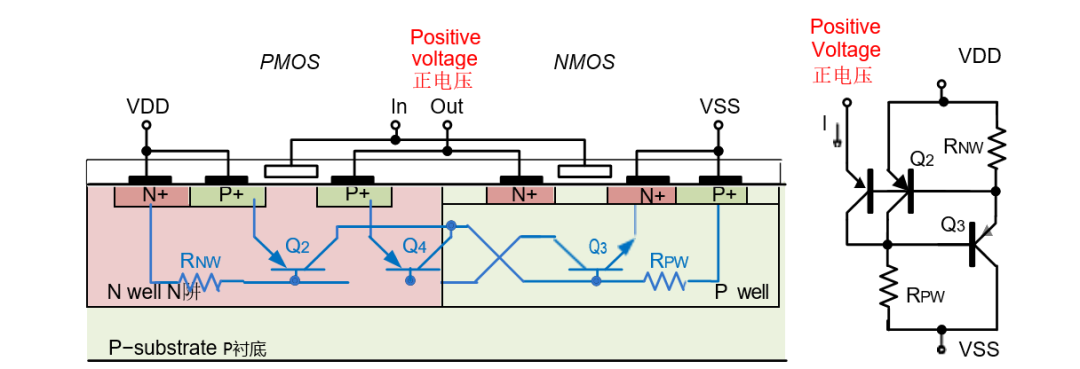

當(dāng)寄生 PNP 和 NPN 雙極晶體管相互作用,在電源軌和接地之間形成低阻抗路徑時(shí),CMOS IC 中就會(huì)出現(xiàn)閂鎖效應(yīng)(Latch-up)。這會(huì)形成一個(gè)具有正反饋的可控硅整流器(SCR),導(dǎo)致過大的電流流動(dòng),并可能造成永久性器件損壞。圖 1 顯示了標(biāo)準(zhǔn) CMOS 逆變器的布局截面圖。圖中還包含寄生 NPN 和 PNP 晶體管。正常工作時(shí),所有結(jié)均為反向偏置。

圖 1. 帶標(biāo)記的寄生雙極晶體管逆變器截面圖和寄生雙極晶體管示意圖

閂鎖效應(yīng)的激活主要取決于寄生 NPN 和 PNP 晶體管的 β 值,以及 N - 阱、P - 阱和襯底電阻。隨著溫度的升高,雙極晶體管的直流電流增益(β)以及阱和襯底的電阻也會(huì)增加。

在高溫條件下,閂鎖效應(yīng)靈敏度的增加也可以視為雙極結(jié)型晶體管(BJT)閾值電壓的降低,從而更容易在阱和襯底電阻上產(chǎn)生足以激活寄生雙極晶體管的壓降。基極 - 發(fā)射極電壓隨溫度變化降低的幅度約為 -2mV/℃,當(dāng)溫度從 25℃升至 200℃時(shí),基極 - 發(fā)射極電壓降低 350mV。室溫下的典型閾值電壓為 0.7V,這意味著閾值電壓大約減半。

5.加速損耗機(jī)制

Arrhenius 定律在可靠性工程中被廣泛用于模擬溫度對(duì)材料和元器件失效率的影響。

其中,R( T) 是速率常數(shù),Ea 是活化能,k 是玻爾茲曼常數(shù)(8.617 · 10?5eV/K),T 為絕對(duì)溫度(單位:開爾文)。通常,每升高10°C可靠性就會(huì)降低一半。

?經(jīng)時(shí)擊穿-TDDB

TDDB 是電子器件中的一種失效機(jī)制,其中介電材料(例如 MOS 晶體管中的柵氧化層)由于長(zhǎng)時(shí)間暴露于電場(chǎng)下而隨時(shí)間退化,導(dǎo)致泄漏電流增加。當(dāng)電壓促使高能電子流動(dòng)時(shí),在氧化層內(nèi)部形成導(dǎo)電路徑,同時(shí)產(chǎn)生陷阱和缺陷。當(dāng)這些導(dǎo)電路徑在氧化層中造成短路時(shí),介電層就會(huì)失效。失效時(shí)間 TF 隨著溫度的升高而呈指數(shù)級(jí)減少。

?負(fù) / 正偏置溫度不穩(wěn)定性 - NBTI / PBTI

NBTI 影響以負(fù)柵極 - 源極電壓工作的 p 溝道 MOS 器件,而 PBTI 則影響處于積累區(qū)的 NMOS 晶體管。在柵極偏壓下,缺陷和陷阱會(huì)增加,導(dǎo)致閾值電壓升高,漏極電流和跨導(dǎo)減少。這種退化顯示出對(duì)數(shù)時(shí)間依賴性和指數(shù)溫度上升,在高于 125°C 時(shí)有部分恢復(fù)。

?電遷移

電遷移是指導(dǎo)體中的金屬原子因電流流動(dòng)而逐漸移位,形成空隙和小丘。因此,如果金屬線中形成的空隙大到足以切斷金屬線,就會(huì)導(dǎo)致開路;如果這些凸起延伸得足夠長(zhǎng)以至于在受影響的金屬與相鄰的另一金屬之間形成橋接,則可能導(dǎo)致短路。電遷移會(huì)隨著電流密度和溫度的升高而加快,尤其是在空隙形成后,會(huì)導(dǎo)致電流擁擠和局部發(fā)熱。金屬線發(fā)生故障的概率與溫度成指數(shù)關(guān)系,與電流密度成平方關(guān)系,與導(dǎo)線長(zhǎng)度成線性關(guān)系。銅互連器件可承受的電流密度約為鋁的五倍,同時(shí)可靠性相似。

?熱載流子退化

當(dāng)溝道電子在 MOS 晶體管漏極附近的高電場(chǎng)中加速,會(huì)發(fā)生熱載流子退化。在柵極氧化層中產(chǎn)生界面態(tài)、陷阱或空穴。它影響諸如閾值電壓 VT、電流增益 β、導(dǎo)通電阻 RDS_ON 和亞閾值泄漏等參數(shù)。在較高溫度下,平均自由程減少,降低了載流子獲得的能量,使得熱載流子退化在低溫條件下更為顯著。

推薦閱讀:

普通鐵磁材料對(duì)3D打印磁環(huán)EMI抑制性能的影響與優(yōu)化路徑

3D打印微型磁環(huán)成本優(yōu)化:多維度降本策略解析

雙核異構(gòu)+TSN+NPU三連擊!意法新款STM32MP23x重塑工業(yè)邊緣計(jì)算格局

聚焦智能聽力健康智能化,安森美北京聽力學(xué)大會(huì)展示創(chuàng)新解決方案